# JTAG debug interface for GNU Debugger

# PPC4xx / APM8xxxx

# **User Manual**

Manual Version 1.07 for BDI3000

# ldiGDB for BDI3000 (PPC4xx / APM8xxxx)

| 1 | Introduction                                                          | 4  |

|---|-----------------------------------------------------------------------|----|

|   | 1.1 BDI3000                                                           | 4  |

|   | 1.2 BDI Configuration                                                 | 5  |

| ~ |                                                                       | •  |

| 2 | Installation                                                          |    |

|   | 2.1 Connecting the BDI3000 to Target                                  |    |

|   | 2.2 Connecting the BDI3000 to Power Supply                            |    |

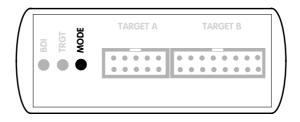

|   | 2.3 Status LED «MODE»                                                 |    |

|   | 2.4 Connecting the BDI3000 to Host                                    |    |

|   | 2.4.1 Serial line communication                                       |    |

|   | 2.4.2 Ethernet communication                                          |    |

|   | 2.5 Installation of the Configuration Software                        |    |

|   | 2.5.1 Configuration with a Linux / Unix host                          |    |

|   | 2.5.2 Configuration with a Windows host                               |    |

|   | 2.5.3 Configuration via Telnet / TFTP                                 |    |

|   | 2.6 Testing the BDI3000 to host connection                            |    |

|   | 2.7 TFTP server for Windows                                           | 19 |

| 3 | Using bdiGDB                                                          | 20 |

| U | •                                                                     |    |

|   | 3.1 Principle of operation                                            |    |

|   | 3.2 Configuration File                                                |    |

|   | 3.2.1 Part [INIT]<br>3.2.2 Part [TARGET]                              |    |

|   |                                                                       |    |

|   | 3.2.3 Part [HOST]                                                     |    |

|   | 3.2.4 Part [FLASH]                                                    |    |

|   | 3.2.5 Part [REGS]                                                     |    |

|   | 3.3 Debugging with GDB                                                |    |

|   | 3.3.1 Target setup                                                    |    |

|   | 3.3.2 Connecting to the target                                        |    |

|   | 3.3.3 Breakpoint Handling                                             |    |

|   | 3.3.4 GDB monitor command                                             |    |

|   | 3.3.5 Target serial I/O via BDI                                       |    |

|   | 3.3.6 Embedded Linux MMU Support                                      |    |

|   | <ul><li>3.4 Telnet Interface</li><li>3.5 Multi-Core Support</li></ul> |    |

|   | ••                                                                    |    |

|   | 3.6 Low level JTAG mode                                               | 54 |

| 4 | Specifications                                                        | 55 |

|   | •                                                                     |    |

| 5 | Environmental notice                                                  | 56 |

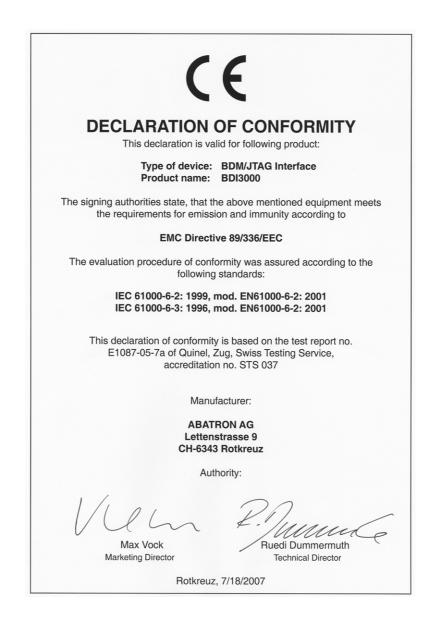

| 6 | Declaration of Conformity (CE)                                        | 56 |

| 0 |                                                                       |    |

| 7 | Warranty and Support Terms                                            | 57 |

|   | 7.1 Hardware                                                          | 57 |

|   | 7.2 Software                                                          |    |

|   | 7.3 Warranty and Disclaimer                                           |    |

|   | 7.4 Limitation of Liability                                           |    |

|   |                                                                       |    |

# Appendices

| Α | Troubleshooting | . 58 |

|---|-----------------|------|

| в | Maintenance     | . 59 |

| С | Trademarks      | . 59 |

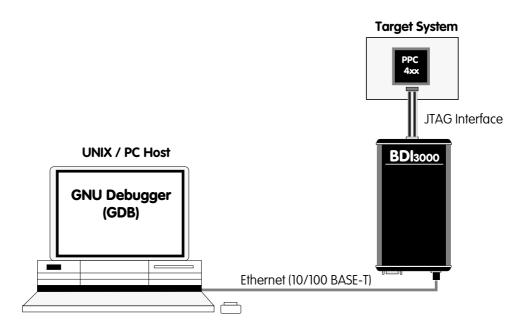

bdiGDB enhances the GNU debugger (GDB), with JTAG debugging for PowerPC 4xx based targets. With the built-in Ethernet interface you get a very fast code download speed. No target communication channel (e.g. serial line) is wasted for debugging purposes. Even better, you can use fast Ethernet debugging with target systems without network capability. The host to BDI communication uses the standard GDB remote protocol.

An additional Telnet interface is available for special debug tasks (e.g. force a hardware reset, program flash memory).

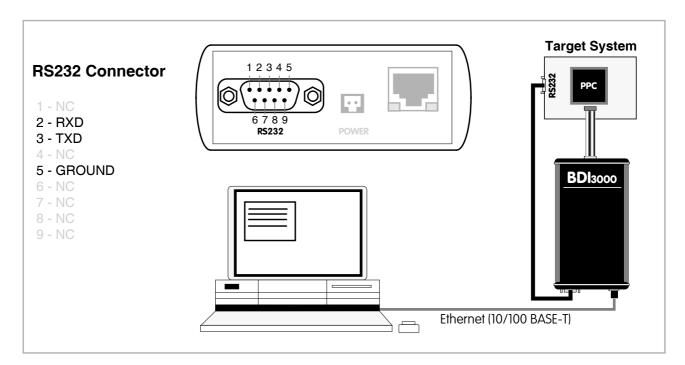

The following figure shows how the BDI3000 interface is connected between the host and the target:

# 1.1 BDI3000

The BDI3000 is the main part of the bdiGDB system. This small box implements the interface between the JTAG pins of the target CPU and a 10/100Base-T Ethernet connector. The firmware of the BDI3000 can be updated by the user with a simple Linux/Windows configuration program or interactively via Telnet/TFTP. The BDI3000 supports 1.2 - 5.0 Volts target systems.

# 1.2 BDI Configuration

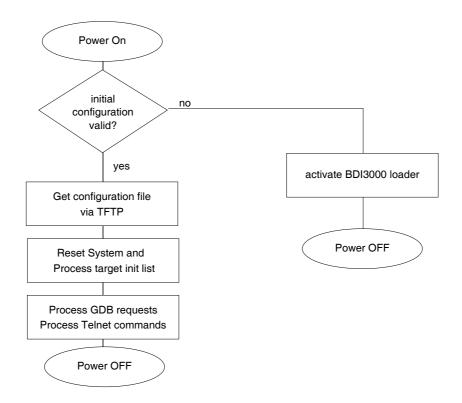

As an initial setup, the IP address of the BDI3000, the IP address of the host with the configuration file and the name of the configuration file is stored within the flash of the BDI3000. Every time the BDI3000 is powered on, it reads the configuration file via TFTP.

Following an example of a typical configuration file:

```

;bdiGDB configuration file for IBM 405GP Reference Board

; -----

[INIT]

; init core register

WSPR 954 0x0000000;DCWR: Disable data cache write-thru

1018 0x0000000;DCCR: Disable data cache

WSPR

1019 0x0000000;ICCR: Disable instruction cache

WSPR

0x0000000;EVPR: Exception Vector Table @0x0000000

982

WSPR

; Setup Peripheral Bus

WDCR 18 0x0000010;Select PB0AP

WDCR 19

0x9B015480;PB0AP: Flash and SRAM

WDCR 18

0x00000000;Select PB0CR

0xFFF18000;PB0CR: 1MB at 0xFFF00000, r/w, 8bit

WDCR 19

; Setup SDRAM Controller

WDCR 16 0x0000080;Select SDTR1

WDCR 17

0x0086400D;SDTR1: SDRAM Timing Register

WDCR 16

0x00000040;Select MB0CF

WDCR 17

0x00046001;MB0CF: 16MB @ 0x0000000

0x00000048;Select MB2CF

WDCR 16

WDCR 17

0x01046001;MB2CF: 16MB @ 0x01000000

0x00000030;Select RTR

WDCR 16

WDCR

17

0x05F00000;RTR: Refresh Timing Register

WDCR

16

0x00000020;Select MCOPT1

WDCR 17

0x80800000;MCOPT1: Enable SDRAM Controller

[TARGET]

0

;use 32 MHz JTAG clock

JTAGCLOCK

405

CPUTYPE

;the used target CPU type

AGENT ; the BDI working mode (LOADONLY | AGENT)

BDIMODE

BREAKMODE SOFT

;SOFT or HARD, HARD uses PPC hardware breakpoint

CATCH ; catch unhandled exceptions

VECTOR

[HOST]

151.120.25.115

ΤP

E:\cyqnus\root\usr\demo\evb405\vxworks

FILE

FORMAT

ELF

;load code MANUAL or AUTO after reset

LOAD

MANUAL

DEBUGPORT 2001

[FLASH]

WORKSPACE 0x00004000 ;workspace in target RAM for fast programming algorithm

CHIPTYPE AM29F ;Flash type (AM29F | AM29BX8 | AM29BX16 | I28BX8 | I28BX16)

CHIPSIZE 0x80000

;The size of one flash chip in bytes (e.g. AM29F040 = 0x80000)

BUSWIDTH 8

;The width of the flash memory bus in bits (8 | 16 | 32)

FILE

E:\cygnus\root\usr\demo\evb405\evb405gp.hex ;The file to program

ERASE

0xFFF80000 ;erase sector 0 of flash in U7 (AM29F040)

ERASE

0xFFF90000 ;erase sector 1 of flash

```

Based on the information in the configuration file, the target is automatically initialized after every reset.

# **2** Installation

# 2.1 Connecting the BDI3000 to Target

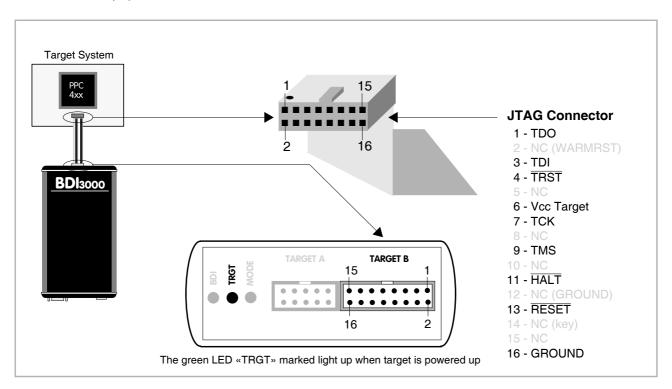

The cable to the target system is a 16 pin flat ribbon cable. In case where the target system has an appropriate connector, the cable can be directly connected. The pin assignment is in accordance with the PowerPC 4xx JTAG connector specification.

In order to ensure reliable operation of the BDI (EMC, runtimes, etc.) the target cable length must not exceed 20 cm (8").

For BDI TARGET B connector signals see table on next page.

#### Warning:

Before you can use the BDI3000 with an other target processor type (e.g. PPC <--> ARM), a new setup has to be done (see chapter 2.5). During this process the target cable must be disconnected from the target system.

To avoid data line conflicts, the BDI3000 must be disconnected from the target system while programming a new firmware for an other target CPU.

## **BDI TARGET B Connector Signals:**

| Pin | Name                  | Description                                                                                                                                                                                                                                                                                        |

|-----|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TDO                   | JTAG Test Data Out<br>This input to the BDI3000 connects to the target TDO pin.                                                                                                                                                                                                                    |

| 2   | <reserved></reserved> |                                                                                                                                                                                                                                                                                                    |

| 3   | TDI                   | JTAG Test Data In<br>This output of the BDI3000 connects to the target TDI pin.                                                                                                                                                                                                                    |

| 4   | TRST                  | JTAG Test Reset<br>This output of the BDI3000 resets the JTAG TAP controller on the target.                                                                                                                                                                                                        |

| 5   | <reserved></reserved> |                                                                                                                                                                                                                                                                                                    |

| 6   | Vcc Target            | <b>1.2 – 5.0V:</b><br>This is the target reference voltage. It indicates that the target has power and it is also used to create the logic-level reference for the input comparators. It also controls the output logic levels to the target. It is normally fed from Vdd I/O on the target board. |

| 7   | тск                   | JTAG Test Clock<br>This output of the BDI3000 connects to the target TCK pin.                                                                                                                                                                                                                      |

| 8   | <reserved></reserved> |                                                                                                                                                                                                                                                                                                    |

| 9   | TMS                   | JTAG Test Mode Select<br>This output of the BDI3000 connects to the target TMS line.                                                                                                                                                                                                               |

| 10  | <reserved></reserved> |                                                                                                                                                                                                                                                                                                    |

| 11  | HALT                  | Processor Halt<br>This output of the BDI3000 connects to the target HALT line.                                                                                                                                                                                                                     |

| 12  | GROUND                | System Ground                                                                                                                                                                                                                                                                                      |

| 13  | RESET                 | System Reset (optional)<br>This open collector output of the BDI3000 is used to hard reset the target system. This is<br>an optional signal and only driven if RESET HARD is selected in the BDI configuration. The<br>standard IBM debug connected specification does not include this signal.    |

| 14  | <reserved></reserved> |                                                                                                                                                                                                                                                                                                    |

| 15  | <reserved></reserved> |                                                                                                                                                                                                                                                                                                    |

| 16  | GROUND                | System Ground                                                                                                                                                                                                                                                                                      |

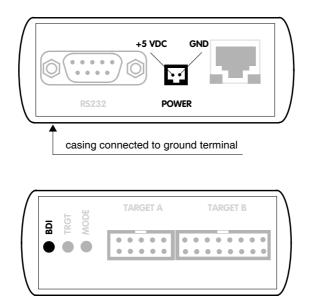

# 2.2 Connecting the BDI3000 to Power Supply

The BDI3000 needs to be supplied with the enclosed power supply from Abatron (5VDC).

Before use, check if the mains voltage is in accordance with the input voltage printed on power supply. Make sure that, while operating, the power supply is not covered up and not situated near a heater or in direct sun light. Dry location use only.

For error-free operation, the power supply to the BDI3000 must be between 4.75V and 5.25V DC. The maximal tolerable supply voltage is 5.25 VDC. Any higher voltage or a wrong polarity might destroy the electronics.

The green LED «BDI» marked light up when 5V power is connected to the BDI3000

#### Please switch on the system in the following sequence:

- 1 -> external power supply

- 2 -> target system

## 2.3 Status LED «MODE»

The built in LED indicates the following BDI states:

| MODE LED | BDI STATES                                                                                     |

|----------|------------------------------------------------------------------------------------------------|

| OFF      | The BDI is ready for use, the firmware is already loaded.                                      |

| ON       | The output voltage from the power supply is too low.                                           |

| BLINK    | The BDI «loader mode» is active (an invalid firmware is loaded or loading firmware is active). |

# 2.4 Connecting the BDI3000 to Host

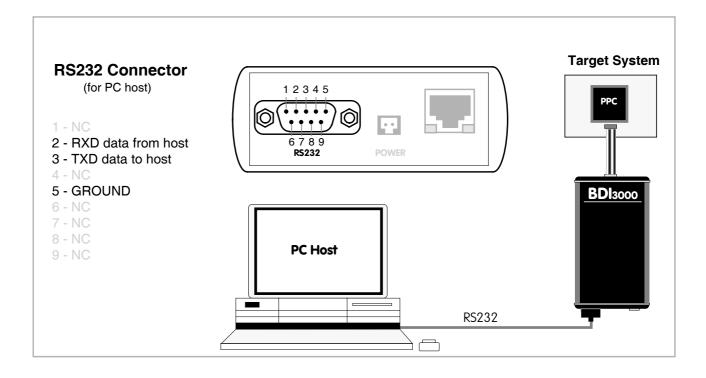

## 2.4.1 Serial line communication

Serial line communication is only used for the initial configuration of the bdiGDB system.

The host is connected to the BDI through the serial interface (COM1...COM4). The communication cable (included) between BDI and Host is a serial cable. There is the same connector pinout for the BDI and for the Host side (Refer to Figure below).

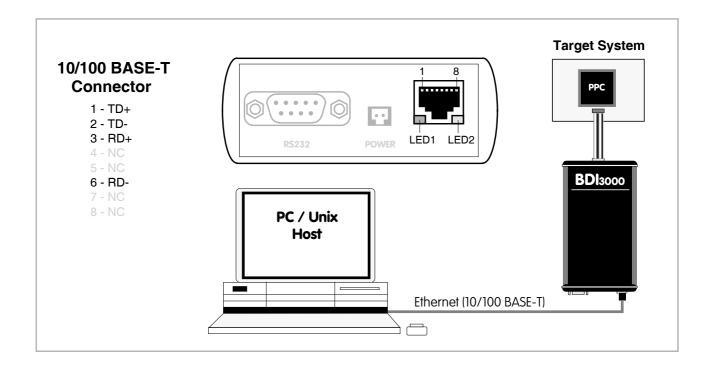

## 2.4.2 Ethernet communication

The BDI3000 has a built-in 10/100 BASE-T Ethernet interface (see figure below). Connect an UTP (Unshielded Twisted Pair) cable to the BD3000. Contact your network administrator if you have questions about the network.

The following explains the meanings of the built-in LED lights:

| LED              | Function        | Description                                                                                                                                                                                           |

|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED 1<br>(green) | Link / Activity | When this LED light is ON, data link is successful between the UTP port<br>of the BDI3000 and the hub to which it is connected.<br>The LED blinks when the BDI3000 is receiving or transmitting data. |

| LED 2<br>(amber) | Speed           | When this LED light is ON, 100Mb/s mode is selected (default).<br>When this LED light is OFF, 10Mb/s mode is selected                                                                                 |

# 2.5 Installation of the Configuration Software

On the enclosed diskette you will find the BDI configuration software and the firmware required for the BDI3000. For Windows users there is also a TFTP server included.

The following files are on the diskette.

| b30pp4gd.exe | Windows Configuration program                                   |

|--------------|-----------------------------------------------------------------|

| b30pp4gd.xxx | Firmware for the BDI3000                                        |

| tftpsrv.exe  | TFTP server for Windows (WIN32 console application)             |

| *.cfg        | Configuration files                                             |

| *.def        | Register definition files                                       |

| bdisetup.zip | ZIP Archive with the Setup Tool sources for Linux / UNIX hosts. |

#### Overview of an installation / configuration process:

- Create a new directory on your hard disk

- Copy the entire contents of the enclosed diskette into this directory

- Linux only: extract the setup tool sources and build the setup tool

- Use the setup tool or Telnet (default IP) to load/update the BDI firmware **Note**: A new BDI has no firmware loaded.

- Use the setup tool or Telnet (default IP) to load the initial configuration parameters

- IP address of the BDI.

- IP address of the host with the configuration file.

- Name of the configuration file. This file is accessed via TFTP.

- Optional network parameters (subnet mask, default gateway).

#### **Activating BOOTP:**

The BDI can get the network configuration and the name of the configuration file also via BOOTP. For this simple enter 0.0.0.0 as the BDI's IP address (see following chapters). If present, the subnet mask and the default gateway (router) is taken from the BOOTP vendor-specific field as defined in RFC 1533.

With the Linux setup tool, simply use the default parameters for the -c option: [root@LINUX\_1 bdisetup]# ./bdisetup -c -p/dev/ttyS0 -b57

The MAC address is derived from the serial number as follows: MAC: 00-0C-01-xx-xx-xx , replace the xx-xx-xx with the 6 left digits of the serial number Example: SN# 33123407 ==>> 00-0C-01-33-12-34

#### Default IP: 192.168.53.72

Before the BDI is configured the first time, it has a default IP of 192.168.53.72 that allows an initial configuration via Ethernet (Telnet or Setup Tools). If your host is not able to connect to this default IP, then the initial configuration has to be done via the serial connection.

## 2.5.1 Configuration with a Linux / Unix host

The firmware update and the initial configuration of the BDI3000 is done with a command line utility. In the ZIP Archive bdisetup.zip are all sources to build this utility. More information about this utility can be found at the top in the bdisetup.c source file. There is also a make file included. Starting the tool without any parameter displays information about the syntax and parameters.

# To avoid data line conflicts, the BDI3000 must be disconnected from the target system while programming the firmware for an other target CPU family.

Following the steps to bring-up a new BDI3000:

#### 1. Build the setup tool:

The setup tool is delivered only as source files. This allows to build the tool on any Linux / Unix host. To build the tool, simply start the make utility.

[root@LINUX\_1 bdisetup]# make cc -02 -c -o bdisetup.o bdisetup.c cc -02 -c -o bdicnf.o bdicnf.c cc -02 -c -o bdidll.o bdidll.c cc -s bdisetup.o bdicnf.o bdidll.o -o bdisetup

#### 2. Check the serial connection to the BDI:

With "bdisetup -v" you may check the serial connection to the BDI. The BDI will respond with information about the current loaded firmware and network configuration.

Note: Login as root, otherwise you probably have no access to the serial port.

```

$ ./bdisetup -v -p/dev/ttyS0 -b115

BDI Type : BDI3000 (SN: 30000154)

Loader : V1.00

Firmware : unknown

MAC : ff-ff-ff-ff-ff

IP Addr : 255.255.255.255

Subnet : 255.255.255.255

Gateway : 255.255.255.255

Host IP : 255.255.255.255

Config : ÿÿÿÿÿÿ......

```

#### 3. Load/Update the BDI firmware:

With "bdisetup -u" the firmware is programmed into the BDI3000 flash memory. This configures the BDI for the target you are using. Based on the parameters -a and -t, the tool selects the correct firmware file. If the firmware file is in the same directory as the setup tool, there is no need to enter a -d parameter.

```

$ ./bdisetup -u -p/dev/ttyS0 -b115 -aGDB -tPPC400

Connecting to BDI loader

Programming firmware with ./b30pp4gd.100

Erasing firmware flash ....

Erasing firmware flash passed

Programming firmware flash ....

Programming firmware flash passed

```

#### 4. Transmit the initial configuration parameters:

With "bdisetup -c" the configuration parameters are written to the flash memory within the BDI. The following parameters are used to configure the BDI:

| BDI IP Address           | The IP address for the BDI3000. Ask your network administrator for as-<br>signing an IP address to this BDI3000. Every BDI3000 in your network<br>needs a different IP address.                                                                                                                                                                      |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subnet Mask              | The subnet mask of the network where the BDI is connected to. A subnet mask of 255.255.255.255 disables the gateway feature. Ask your network administrator for the correct subnet mask. If the BDI and the host are in the same subnet, it is not necessary to enter a subnet mask.                                                                 |

| Default Gateway          | Enter the IP address of the default gateway. Ask your network administra-<br>tor for the correct gateway IP address. If the gateway feature is disabled,<br>you may enter 255.255.255.255 or any other value.                                                                                                                                        |

| Config - Host IP Address | Enter the IP address of the host with the configuration file. The configura-<br>tion file is automatically read by the BDI after every start-up via TFTP.<br>If the host IP is 255.255.255.255 then the setup tool stores the configura-<br>tion read from the file into the BDI internal flash memory. In this case no<br>TFTP server is necessary. |

| Configuration file       | Enter the full path and name of the configuration file. This file is read by the setup tool or via TFTP. Keep in mind that TFTP has it's own root directory (usual /tftpboot).                                                                                                                                                                       |

```

$ ./bdisetup -c -p/dev/ttyS0 -b115 \

> -i151.120.25.102 \

> -h151.120.25.112 \

> -fe:/bdi3000/mytarget.cfg

Connecting to BDI loader

Writing network configuration

Configuration passed

```

#### 5. Check configuration and exit loader mode:

The BDI is in loader mode when there is no valid firmware loaded or you connect to it with the setup tool. While in loader mode, the Mode LED is blinking. The BDI will not respond to network requests while in loader mode. To exit loader mode, the "bdisetup -v -s" can be used. You may also power-off the BDI, wait some time (1min.) and power-on it again to exit loader mode.

```

$ ./bdisetup -v -p/dev/ttyS0 -b115 -s

BDI Type : BDI3000 (SN: 30000154)

Loader : V1.00

Firmware : V1.00 bdiGDB for PPC400

MAC : 00-0c-01-30-00-01

IP Addr : 151.120.25.102

Subnet : 255.255.255.255

Gateway : 255.255.255

Host IP : 151.120.25.112

Config : /bdi3000/mytarget.cfg

```

The Mode LED should go off, and you can try to connect to the BDI via Telnet.

```

$ telnet 151.120.25.102

```

## 2.5.2 Configuration with a Windows host

First make sure that the BDI is properly connected (see Chapter 2.1 to 2.4).

To avoid data line conflicts, the BDI3000 must be disconnected from the target system while programming the firmware for an other target CPU family.

| BDI3000 Update/Setup                                           | x                                                             |  |

|----------------------------------------------------------------|---------------------------------------------------------------|--|

| Connect BDI3000 Loader<br>Channel<br>Port COM1<br>Speed 115200 | SN: 30000154<br>MAC: 000C01300001<br>Version: 1.00<br>Connect |  |

| BD13000 Firmware                                               |                                                               |  |

| Loaded Version: 1.00<br>Newest Version: 1.00                   |                                                               |  |

| Current Erase                                                  | Update                                                        |  |

| - Configuration                                                |                                                               |  |

| BDI IP Address                                                 | 151.120.25.102                                                |  |

| Subnet Mask                                                    | 255.255.255.0                                                 |  |

| Default Gateway                                                | 255.255.255.255                                               |  |

| Config - Host IP Address                                       | 151.120.25.112                                                |  |

| Configuration file<br>/bdi3000/mytarget.cfg                    |                                                               |  |

| Cancel Ok                                                      | Transmit                                                      |  |

| Writing setup data passed                                      |                                                               |  |

dialog box «BDI3000 Update/Setup»

Before you can use the BDI3000 together with the GNU debugger, you must store the initial configuration parameters in the BDI3000 flash memory. The following options allow you to do this:

| Port    | Select the communication port where the BDI3000 is connected during<br>this setup session. If you select Network, make sure the Loader is already<br>active (Mode LED blinking). If there is already a firmware loaded and run-<br>ning, use the Telnet command "boot loader" to activate Loader Mode. |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Speed   | Select the baudrate used to communicate with the BDI3000 loader during this setup session.                                                                                                                                                                                                             |

| Connect | Click on this button to establish a connection with the BDI3000 loader.<br>Once connected, the BDI3000 remains in loader mode until it is restarted<br>or this dialog box is closed.                                                                                                                   |

| Current | Press this button to read back the current loaded BDI3000 firmware ver-<br>sion. The current firmware version will be displayed.                                                                                                                                                                       |

| Erase                    | Press this button to erase the current loaded firmware.                                                                                                                                                                                                                                                                                              |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Update                   | This button is only active if there is a newer firmware version present in the execution directory of the bdiGDB setup software. Press this button to write the new firmware into the BDI3000 flash memory.                                                                                                                                          |

| BDI IP Address           | Enter the IP address for the BDI3000. Use the following format:<br>xxx.xxx.xxx e.g.151.120.25.101<br>Ask your network administrator for assigning an IP address to this<br>BDI3000. Every BDI3000 in your network needs a different IP address.                                                                                                      |

| Subnet Mask              | Enter the subnet mask of the network where the BDI is connected to.<br>Use the following format: xxx.xxx.xxxe.g.255.255.255.0<br>A subnet mask of 255.255.255.255 disables the gateway feature.<br>Ask your network administrator for the correct subnet mask.                                                                                       |

| Default Gateway          | Enter the IP address of the default gateway. Ask your network administra-<br>tor for the correct gateway IP address. If the gateway feature is disabled,<br>you may enter 255.255.255 or any other value.                                                                                                                                            |

| Config - Host IP Address | Enter the IP address of the host with the configuration file. The configura-<br>tion file is automatically read by the BDI after every start-up via TFTP.<br>If the host IP is 255.255.255.255 then the setup tool stores the configura-<br>tion read from the file into the BDI internal flash memory. In this case no<br>TFTP server is necessary. |

| Configuration file       | Enter the full path and name of the configuration file. This file is read by the setup tool or via TFTP.                                                                                                                                                                                                                                             |

| Transmit                 | Click on this button to store the configuration in the BDI3000 flash memory.                                                                                                                                                                                                                                                                         |

#### Note:

Using this setup tool via the Network channel is only possible if the BDI3000 is already in Loader mode (Mode LED blinking). To force Loader mode, enter "boot loader" at the Telnet. The setup tool tries first to establish a connection to the Loader via the IP address present in the "BDI IP Address" entry field. If there is no connection established after a time-out, it tries to connect to the default IP (192.168.53.72).

# 2.5.3 Configuration via Telnet / TFTP

The firmware update and the initial configuration of the BDI3000 can also be done interactively via a Telnet connection and a running TFTP server on the host with the firmware file. In cases where it is not possible to connect to the default IP, the initial setup has to be done via a serial connection.

# To avoid data line conflicts, the BDI3000 must be disconnected from the target system while programming the firmware for an other target CPU family.

Following the steps to bring-up a new BDI3000 or updating the firmware. Connect to the BDI Loader via Telnet. If a firmware is already running enter "boot loader" and reconnect via Telnet.

\$ telnet 192.168.53.72

or

\$ telnet <your BDI IP address>

Update the network parameters so it matches your needs:

```

LDR>network

: 00-0c-01-30-00-01

BDI MAC

: 192.168.53.72

BDI IP

BDI Subnet : 255.255.255.0

BDI Gateway : 255.255.255.255

Config IP

: 255.255.255.255

Config File :

LDR>netip 151.120.25.102

LDR>nethost 151.120.25.112

LDR>netfile /bdi3000/mytarget.cfg

LDR>network

BDI MAC

: 00-0c-01-30-00-01

BDI IP

: 151.120.25.102

BDI Subnet : 255.255.255.0

BDI Gateway : 255.255.255.255

: 151.120.25.112

Config IP

Config File : /bdi3000/mytarget.cfg

LDR>network save

saving network configuration ... passed

BDI MAC : 00-0c-01-30-00-01

BDI IP

: 151.120.25.102

BDI Subnet : 255.255.255.0

BDI Gateway : 255.255.255.255

Config IP : 151.120.25.112

Config File : /bdi3000/mytarget.cfg

```

#### In case the subnet has changed, reboot before trying to load the firmware

LDR>boot loader

Connect again via Telnet and program the firmware into the BDI flash:

```

$ telnet 151.120.25.102

LDR>info

BDI Firmware: not loaded

BDI CPLD ID : 01285043

BDI CPLD UES: fffffff

: 00-0c-01-30-00-01

BDI MAC

BDI IP

: 151.120.25.102

BDI Subnet : 255.255.255.0

BDI Gateway : 255.255.255.255

Config IP : 151.120.25.112

Config File : /bdi3000/mytarget.cfg

LDR>fwload e:/temp/b30pp4gd.100

erasing firmware flash ... passed

programming firmware flash ... passed

LDR>info

BDI Firmware: 22 / 1.00

BDI CPLD ID : 01285043

BDI CPLD UES: fffffff

BDI MAC : 00-0c-01-30-00-01

BDI IP

: 151.120.25.102

BDI Subnet : 255.255.255.0

BDI Gateway : 255.255.255.255

Config IP

: 151.120.25.112

Config File : /bdi3000/mytarget.cfg

```

LDR>

To boot now into the firmware use:

LDR>boot

The Mode LED should go off, and you can try to connect to the BDI again via Telnet.

telnet 151.120.25.102

## 2.6 Testing the BDI3000 to host connection

After the initial setup is done, you can test the communication between the host and the BDI3000. There is no need for a target configuration file and no TFTP server is needed on the host.

- If not already done, connect the BDI3000 system to the network.

- Power-up the BDI3000.

- Start a Telnet client on the host and connect to the BDI3000 (the IP address you entered during initial configuration).

- If everything is okay, a sign on message like «BDI Debugger for Embedded PowerPC» and a list of the available commands should be displayed in the Telnet window.

## 2.7 TFTP server for Windows

The bdiGDB system uses TFTP to access the configuration file and to load the application program. Because there is no TFTP server bundled with Windows, Abatron provides a TFTP server application **tftpsrv.exe**. This WIN32 console application runs as normal user application (not as a system service).

Command line syntax: tftpsrv [p] [w] [dRootDirectory]

Without any parameter, the server starts in read-only mode. This means, only read access request from the client are granted. This is the normal working mode. The bdiGDB system needs only read access to the configuration and program files.

The parameter [p] enables protocol output to the console window. Try it. The parameter [w] enables write accesses to the host file system. The parameter [d] allows to define a root directory.

| tftpsrv p         | Starts the TFTP server and enables protocol output                                                                                                                                            |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tftpsrv p w       | Starts the TFTP server, enables protocol output and write accesses are allowed.                                                                                                               |

| tftpsrv dC:\tftp\ | Starts the TFTP server and allows only access to files in C:\tftp and its subdirectories. As file name, use relative names.<br>For example "bdi\mpc750.cfg" accesses "C:\tftp\bdi\mpc750.cfg" |

You may enter the TFTP server into the Startup group so the server is started every time you login.

# 3 Using bdiGDB

# 3.1 Principle of operation

The firmware within the BDI handles the GDB request and accesses the target memory or registers via the JTAG interface. There is no need for any debug software on the target system. After loading the code via TFTP, debugging can begin at the very first assembler statement.

Whenever the BDI system is powered-up the following sequence starts:

#### Breakpoints:

There are two breakpoint modes supported. One of them (SOFT) is implemented by replacing application code with a TRAP instruction. The other (HARD) uses the built in breakpoint logic. If HARD is used, only 4 (2 for 401/403) breakpoints can be active at the same time. The following example selects SOFT as the breakpoint mode:

BREAKMODE SOFT ;SOFT or HARD, HARD uses PPC hardware breakpoints

All the time the application is suspended (i.e. caused by a breakpoint) the target processor remains freezed.

# 3.2 Configuration File

The configuration file is automatically read by the BDI after every power on. The syntax of this file is as follows:

```

; comment

[part name]

identifier parameter1 parameter2 ..... parameterN ; comment

identifier parameter1 parameter2 ..... parameterN

.....

[part name]

identifier parameter1 parameter2 ..... parameterN

identifier parameter1 parameter2 ..... parameterN

.....

etc.

```

Numeric parameters can be entered as decimal (e.g. 700) or as hexadecimal (0x80000).

# 3.2.1 Part [INIT]

The part [INIT] defines a list of commands which should be executed every time the target comes out of reset. The commands are used to get the target ready for loading the program file.

| WGPR register value | Write value to the selected general purpose register.registerthe register number 0 31valuethe value to write into the registerExample: WGPR 0 5                                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WSPR register value | Write value to the selected special purpose register.registerthe register numbervaluethe value to write into the registerExample: WSPR 27 0x00001002 ; SRR1 : ME,RI                                                                                                             |

| WDCR register value | Write value to the selected device control register. Some special register<br>numbers are use to access the PPC476 Multi-core debug registers.<br>register the register number<br>value the value to write into the register<br>Example: WDCR 0x12 0x0000010 ; Select EBC0_B0AP |

| WREG name value     | Write value to the selected register/memory by namenamethe case sensitive register name from the reg def filevaluethe value to write to the register/memoryExample: WREG msr 0x00001002                                                                                         |

| WM8 address value   | Write a byte (8bit) to the selected memory place.addressthe memory addressvaluethe value to write to the target memoryExample: WM8 0xFFFFA21 0x04 ; SYPCR: watchdog disable                                                                                                     |

| WM16 address value  | Write a half word (16bit) to the selected memory place.addressthe memory addressvaluethe value to write to the target memoryExample: WM16 0x02200200 0x0002 ; TBSCR                                                                                                             |

| WM32 address value  | Write a word (32bit) to the selected memory place.addressthe memory addressvaluethe value to write to the target memoryExample: WM32 0x02200000 0x01632440 ; SIUMCR                                                                                                             |

| RM8 address value     | Read a byte (8bit) from the selected memory place.<br>address the memory address<br>Example: RM8 0x0000000                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RM16 address value    | Read a half word (16bit) from the selected memory place.<br>address the memory address<br>Example: RM16 0x0000000                                                                                                                                                                                                                                                                                                                        |  |  |

| RM32 address value    | Read a word (32bit) from the selected memory place.<br>address the memory address<br>Example: RM32 0x0000000                                                                                                                                                                                                                                                                                                                             |  |  |

| SIDCR cfgaddr cfgdata | Sets the DCR addresses of the Configuration Address and Data Registerused for Indirectly accessed Device Control Registers.cfgaddrthe address of the Configuration Address Registercfgdatathe address of the Configuration Data RegisterExample:SIDCR 0x10 0x11 ; set SDRAM configurationSIDCR 0x12 0x13 ; set EBC configuration                                                                                                         |  |  |

| WIDCR offset data     | Write to an Indirectly accessed Device Control Register using the Configuration Address and Data Registers define with the last SIDCR entry.offsetoffset of the register, will be written to cfgaddrdatavalue for the register, will be written to cfgdataExample:SIDCR 0x10 0x11 ; set SDRAM ConfigWIDCR 0x0040 0x00007201 ; SDRAM_MB0CFWIDCR 0x0044 0x08007201 ; SDRAM_MB1CFWIDCR 0x0048 0x0000000 ; SDRAM_MB2CF                       |  |  |

| DELAY value           | Delay for the selected time. A delay may be necessary to let the clock PLL<br>lock again after a new clock rate is selected.<br>value the delay time in milliseconds (130000)<br>Example: DELAY 500 ; delay for 0.5 seconds                                                                                                                                                                                                              |  |  |

| MMAP start end        | Because a memory access to an invalid memory space via JTAG leads to<br>a deadlock, this entry can be used to define up to 32 valid memory ranges.<br>If at least one memory range is defined, the BDI checks against this<br>range(s) and avoids accessing of not mapped memory ranges.<br>start the start address of a valid memory range<br>end the end address of this memory range<br>Example: MMAP 0xFFE00000 0xFFFFFFFF ;Boot ROM |  |  |

| MMAP TLB              | Only for 440/464/465: If this entry is present, the BDI checks every mem-<br>ory access against the current TLB setting. This avoids illegal memory ac-<br>cesses. Don't mix the two different MMAP entry types.                                                                                                                                                                                                                         |  |  |

#### Adding entries to the 440/464/465 TLB:

For 440/464/465 cores, it is necessary to setup the TLB before memory can be accessed. This is because the MMU is always enabled. The init list entries STLB/WTLB allows an initial setup of the TLB array. The first WTLB entry also clears the whole TLB array.

| WTLB epn rpn      | array. For param<br>via a Telnet com<br>epn<br>rpn | 4/465 (for 476 see next page): Adds an entry to the TLB<br>neter description see below. A TLB entry can also be addd<br>amand (enter WTLB at the telnet for a description).<br>the effective page number, size and WIMG flags<br>the real page number and access rights<br>TLB 0xF0000095 0x1F00003F ;Boot Space 256MB |

|-------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STLB index attrib | •                                                  | L/465 (for 476 see next page): Sets a new start index, the LB attributes for the following TLB writes (WTLB). the start index of the following TLB writes. defines the TID and some TLB attributes STLB 3 0x0000005 ; Index=3, TID=5                                                                                   |

|                   | Example.                                           | STLB 7 0x00007000 ; Index=7, U1,U2,U3, TID=0                                                                                                                                                                                                                                                                           |

The epn parameter defines the effective page number, endian, space, size and WIMG flags:

| +     |    |   |   | +-     |   |

|-------|----|---|---|--------|---|

| <br>+ |    | • |   | SIZE V |   |

|       | 22 | 1 | 1 | 4      | 4 |

The rpn parameter defines the real page number and access rights:

| ++   |     | ++     |

|------|-----|--------|

| ERPN | RPN | XWRXWR |

| +    |     | ++     |

| 4    | 22  | 6      |

Not all fields of a TLB entry are defined with the above values. The other values except the valid bit are set to zero unless defined with the optional STLB init list entry. The XWRXWR field starts with the user access rights. See also 440/464/465 user's manual part "Memory Management".

The attrib parameter of the STLB entry has the following bit definitions:

+-----+ FWIDID|UUUU|----| TID | +----+ 10 6 4 4 8

The following example clears the TLB and adds two entries to access ROM and SDRAM:

[INIT] ; Setup TLB WTLB 0xF0000095 0x1F00003F ;Boot Space 256MB, cache inhibited, guarded WTLB 0x00000098 0x0000003F ;SDRAM 256MB @0x00000000, write-through

#### Adding entries to the 476 TLB:

For 476 cores, it is necessary to setup the TLB before memory can be accessed. This is because the MMU is always enabled. The init list entries STLB/WTLB allows an initial setup of the TLB array.

| WTLB epn rpn  | Only for 476: Adds an entry to the TLB array. For parameter des see below. A TLB entry can also be addd via a Telnet command WTLB at the telnet for a description). |                                                                             |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|               | epn                                                                                                                                                                 | defines TLB Word 0 [0:27]                                                   |

|               | rpn                                                                                                                                                                 | defines RPN and TLB Word 2 [20:31]                                          |

| STLB way erpn |                                                                                                                                                                     | fines the way, the TID, ERPN and some TLB attributes for<br>B write (WTLB). |

|               | way                                                                                                                                                                 | defines way, bolted and TID                                                 |

|               | erpn                                                                                                                                                                | defines ERPN and TLB Word 2 [0:19]                                          |

The epn parameter defines the effective page number, space and size:

| + |     | -+-+- | +    | -++ |

|---|-----|-------|------|-----|

|   | EPN | V S   | SIZE |     |

| + |     | -+-+- | +    | -++ |

|   | 20  | 1 1   | 6    | 4   |

The rpn parameter defines the real page number, WIMG flags, endian and access rights:

| + |    | ++           |

|---|----|--------------|

|   |    | WIMGE-XWRXWR |

| + | 20 | 12           |

The way parameter selects the way, bolted and TID (see also 476 tlbwe instruction):

| +    | +    | ++ | ++  |  |

|------|------|----|-----|--|

| Www- | Bbbb |    | TID |  |

| +    | +    | ++ | ++  |  |

| 4    | 4    | 8  | 16  |  |

The erpn parameter defines cache flags, user bits and the extended real page number:

| +IDUUUU | •  |

|---------|----|

| +       | 12 |

# 3.2.2 Part [TARGET]

The part [TARGET] defines some target specific values.

| CPUTYPE type [core [sc | This value give<br>FPU for chips v | s the BDI information about the connected CPU/core. Add<br>with integrated floating point unit. Accessing FPU registers<br>bace in target RAM. See WORKSPACE parameter.                                                                |

|------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | type                               | The CPU type from the following list:<br>401, 403, 405, 440, 464, 465, 476, AXX3500<br>APM86xxx, APM86290, APM86190,<br>APM86391, APM86392, APM86491,<br>APM86691, APM86692, APM86771, APM86791                                        |

|                        | core                               | the core number within the SOC (07)                                                                                                                                                                                                    |

|                        | SOC                                | the SOC number (03)                                                                                                                                                                                                                    |

|                        | Example:                           | CPUTYPE 440 FPU<br>#0 CPUTYPE APM86290 0 0<br>#1 CPUTYPE APM86290 1 0                                                                                                                                                                  |

| JTAGCLOCK value        | With this value                    | you select the JTAG clock frequency.                                                                                                                                                                                                   |

|                        | value                              | The JTAG clock frequency in Hertz or an index value from the following table:                                                                                                                                                          |

|                        |                                    | 0 = 32 MHz 6 = 1 MHz 12 = 10 kHz                                                                                                                                                                                                       |

|                        |                                    | 1 = 16 MHz 7 = 500 kHz 13 = 5 kHz                                                                                                                                                                                                      |

|                        |                                    | 2 = 11 MHz 8 = 200 kHz 14 = 2 kHz                                                                                                                                                                                                      |

|                        |                                    | 3 = 8  MHz $9 = 100  kHz$ $15 = 1  kHz4 = 5  MHz$ $10 = 50  kHz5 = 4  MHz$ $11 = 20  kHz$                                                                                                                                              |

|                        | Example:                           | JTAGCLOCK 1 ; JTAG clock is 16 MHz                                                                                                                                                                                                     |

| RESET type [time]      |                                    | et type the BDI uses when reseting the target via the JTAG ia debug connector pin 13.                                                                                                                                                  |

|                        | type                               | NONE, CORE, CHIP, SYSTEM (default)<br>HARD (via debug connector pin 13)                                                                                                                                                                |

|                        | time                               | The time in milliseconds the BDI assert the reset signal.                                                                                                                                                                              |

|                        | Example:                           | RESET CHIP ; IOP480 does not support system reset                                                                                                                                                                                      |

| WAKEUP time            | between forcing                    | e init list allows to define a delay time (in ms) the BDI inserts<br>g a target reset and starting communicating with the target.                                                                                                      |

|                        | time                               | the delay time in milliseconds                                                                                                                                                                                                         |

|                        | Example:                           | WAKEUP 3000 ; insert 3sec wake-up time                                                                                                                                                                                                 |

| MEMDELAY time          | inserts for mem                    | e init list allows to define a delay time (in TCK's) the BDI<br>ory block reads between stuffing the "lwzu" instruction and<br>ded GPR. Maybe used when dumping slow memory.<br>the delay time in multiple of 8 TCK's (default 10 x 8) |

|                        | Example:                           | MEMDELAY 2 ;16 TCK's memory read access delay                                                                                                                                                                                          |

| STARTUP mode [runTim | e] [RUN HALT]                       |                                                                                                                                                                                                          |

|----------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                                     | selects the core startup mode and for APM86xxx if the                                                                                                                                                    |

|                      |                                     | alted after sleep/powerdown.                                                                                                                                                                             |

|                      | The following sta                   | irtup modes are supported:                                                                                                                                                                               |

|                      | HALT                                | This default mode forces the core to debug mode imme-<br>diately out of reset. No code is executed after reset.                                                                                          |

|                      | STOP                                | In this mode, the BDI lets the core execute code for "run-<br>time" milliseconds after reset. This mode is useful when<br>monitor code should initialize the target system.                              |

|                      | RUN                                 | After reset, the core executes code until stopped by the Telnet "halt" command.                                                                                                                          |

|                      | WAIT                                | Same as RUN but don't poll core status until selected via Telnet "select" command.                                                                                                                       |

|                      | [RUN HALT]                          | APM86xxx: Defines if a core should be halted after sleep/powerdown. The default is RUN.                                                                                                                  |

|                      | Example:                            | STARTUP STOP 3000 ; let the CPU run for 3 seconds                                                                                                                                                        |

| BREAKMODE mode       |                                     | defines how breakpoints are implemented. The current e changed via the Telnet interface                                                                                                                  |

|                      | SOFT                                | This is the normal mode. Breakpoints are implemented<br>by replacing code with a TRAP instruction.                                                                                                       |

|                      | HARD                                | In this mode, the PPC breakpoint hardware is used.<br>Only 2 / 4 breakpoints at a time are supported.                                                                                                    |

|                      | Example:                            | BREAKMODE HARD                                                                                                                                                                                           |

| STEPMODE mode        |                                     | lefines how single step (instruction step) is implemented.<br>p mode (HWBP) is useful when stepping instructions that<br>iss exception.                                                                  |

|                      | JTAG                                | This is the default mode. The step feature of the JTAG debug interface is used for single stepping.                                                                                                      |

|                      | HWBP                                | In this mode, one or two hardware breakpoints are used<br>to implement single stepping. Use this mode when de-<br>bugging a Linux kernel.                                                                |

|                      | Example:                            | STEPMODE HWBP                                                                                                                                                                                            |

| REGLIST list         | used. You can d<br>By default STD a | ze the time spent to read registers, this parameter can be<br>efine which register group is really read from the target.<br>and FPR are read and transferred.<br>mes are use to select a register group: |

|                      | STD                                 | The standard register block. The FPR registers are not<br>read from the target but transferred. You can't disable<br>this register group.                                                                |

|                      | FPR                                 | The floating point registers are read and transferred.                                                                                                                                                   |

|                      | SPR                                 | Some additional special purpose register.                                                                                                                                                                |

|                      | ALL                                 | Include all register groups                                                                                                                                                                              |

|                      | Example:                            | REGLIST STD ; only standard registers                                                                                                                                                                    |

| VECTOR CATCH        |                                                                                                                                                                   | is present, the BDI catches all unhandled exceptions.<br>ions is only possible if the vector table is writable.<br>VECTOR CATCH ; catch unhandled exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MMU XLAT [kb]       | present, the BDI<br>net are virtual ac<br>al base address<br>translation. If ne<br>accessing memo<br>For more inform<br>If not zero, the 12<br>bit in a page tabl | ts Linux kernel debugging when MMU is on. If this line is<br>assumes that all addresses received from GDB and Tel-<br>dresses. The optional parameter defines the kernel virtu-<br>(default is 0xC000000) and is used for default address<br>cessary the BDI creates appropriate TLB entries before<br>bry based on information found in the kernel page table.<br>ation see also chapter "Embedded Linux MMU Support".<br>2 lower bits of "kb" defines the position of the page present<br>le entry. By default 0x002 (440: 0x001) is assumed for the<br>. The position depends on the Linux kernel version.<br>The kernel virtual base address (KERNELBASE)<br>MMU XLAT ;enable support for virtual addresses<br>MMU XLAT 0xC000020 ; page present bit is 0x020 |  |

| PTBASE addr         | for the virtual ac                                                                                                                                                | defines the physical memory address where the BDI looks<br>dress of the array with the two page table pointers. For<br>n see also chapter "Embedded Linux MMU Support".<br>Physical address of the memory used to store the virtual<br>address of the array with the two page table pointers.<br>PTBASE 0xf0                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| SIO port [baudrate] | connector. The p<br>host communica<br>Telnet port (23).<br>you should see<br>normal Telnet co                                                                     | a present, a TCP/IP channel is routed to the BDI's RS232<br>port parameter defines the TCP port used for this BDI to<br>ation. You may choose any port except 0 and the default<br>On the host, open a Telnet session using this port. Now<br>the UART output in this Telnet session. You can use the<br>connection to the BDI in parallel, they work completely in-<br>input to the UART is implemented.<br>The TCP/IP port used for the host communication.<br>The BDI supports 2400 115200 baud<br>SIO 7 9600 ;TCP port for virtual IO                                                                                                                                                                                                                         |  |

| WORKSPACE address   |                                                                                                                                                                   | es the floating-point registers, the BDI needs a workspace<br>get RAM. Enter the base address of this RAM area.<br>the address of the RAM area<br>WORKSPACE 0x0000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| HALT [HIGH   LOW]   | With this parameter it is possible to define if the HALT signal is active low (default) or active high.<br>Example: HALT HIGH ;HALT signal is active high         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| CGROUP cores        |                                                                                                                                                                   | gives the BDI information about how to restart multiple<br>ne time in response to a GDB continue command. See<br>ore Support.<br>The selected cores as bitmap.<br>#0 CGROUP 0x0f ;GDB continue core group (restart)<br>#1 CGROUP 0x02 ;GDB continue core group (prepare)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

#### Daisy chained JTAG devices:

For PPC4xx targets, the BDI can also handle systems with multiple devices connected to the JTAG scan chain. In order to put the other devices into BYPASS mode and to count for the additional bypass registers, the BDI needs some information about the scan chain layout. Enter the number (count) and total instruction register (irlen) length of the devices present before the PPC4xx chip (Predecessor). Enter the appropriate information also for the devices following the PPC4xx chip (Successor):

| SCANPRED count irlen | the PPC4xx chip<br>count<br>irlen                                                                             | the BDI information about JTAG devices present before<br>o in the JTAG scan chain.<br>The number of preceding devices (0 31)<br>The sum of the length of all preceding instruction regis-<br>ters (IR) (0 1024)             |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                      | Example:                                                                                                      | SCANPRED 1 8 ; one device with an IR length of 8                                                                                                                                                                            |  |  |

| SCANSUCC count irlen | This value gives the BDI information about JTAG devices present after the PPC4xx chip in the JTAG scan chain. |                                                                                                                                                                                                                             |  |  |

|                      | count                                                                                                         | The number of succeeding devices (0 31)                                                                                                                                                                                     |  |  |

|                      | irlen                                                                                                         | The sum of the length of all succeeding instruction reg-<br>isters (IR) (0 1024)                                                                                                                                            |  |  |

|                      | Example:                                                                                                      | SCANSUCC 2 12 ; two device with an IR length of 8+4                                                                                                                                                                         |  |  |

| SCANMISC len val pos | IR length of a 40 chained ,it need                                                                            | been added to support Xilinx Virtex-II Pro 405 cores. The<br>05 core is 4 (instead of 7) and if the FPGA JTAG is daisy<br>s a special IR value (not bypass). Also the FPGA has ac-<br>register if IR is loaded with 100000. |  |  |

|                      | len                                                                                                           | The length of the 405 IR register (default is 7)                                                                                                                                                                            |  |  |